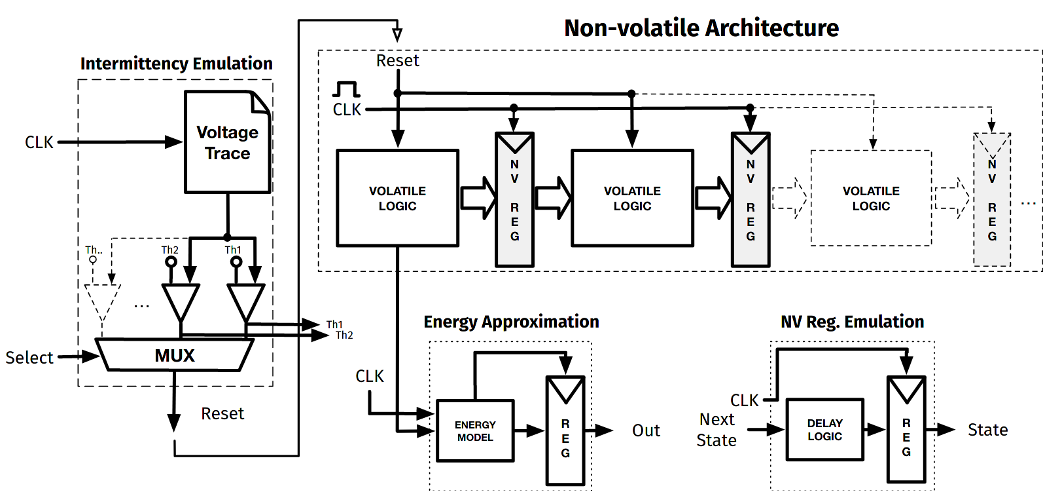

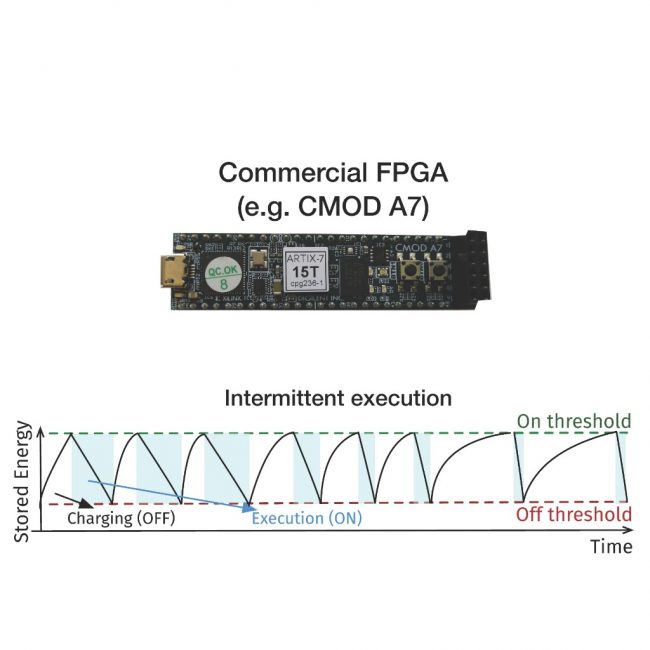

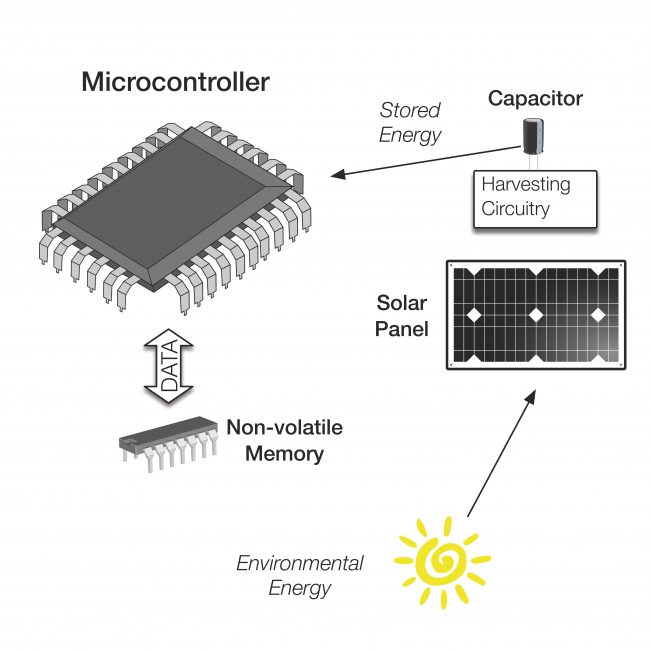

The proposed solution is a new FPGA-based framework that allows to emulate a non-volatile architecture on any type of hardware. This framework can be used for debugging, and functional testing of logic. In addition, it can also be integrated into a yet-to-be-built computing system, so the

whole system can be tested as a whole. With this innovative solution, for the first time, rapid prototyping and validation can be performed on any battery-less hardware architecture.