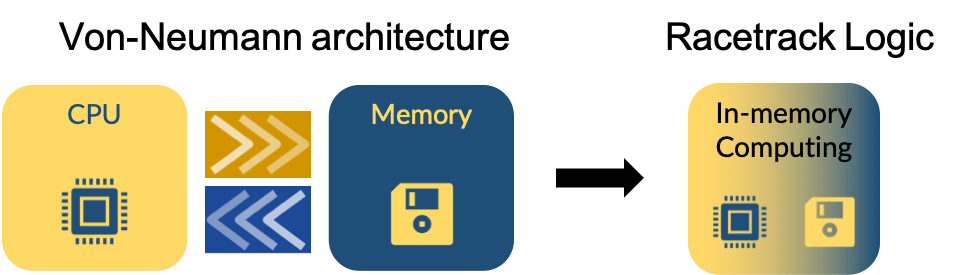

Currently, the computing paradigm adopted in the PCs and Smartphones is based on the Von-Neumann architecture, where a processing unit (CPU) and the memory are present. This organization requires a continous exchange of data between the processor and the memory in order to perform elaboration and dissipates a lot of power.

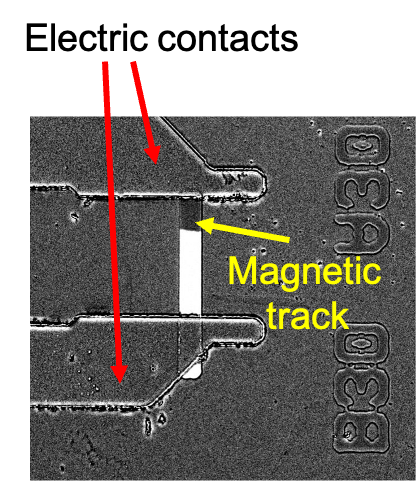

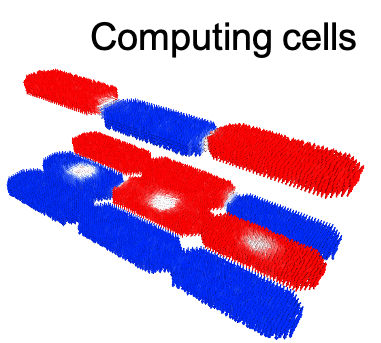

The technology proposed, the racetrack logic, is a non-volatile memory with computing capabilities. The computation is performed directly on the stored data. The proposed device can implement logic functions that cannot be integrated in standard memories.

Moreover, the computation is executed in parallel over the whole array in a single clock cycle, without the need of external circuitry.

Having the possibility to perform the elaboration locally, within the memory, the data transfer between the CPU and the main memory is drastically reduced, especially for data intensive applications. The data transfer is energetically expensive and must be reduced in order to increase the battery life of portable devices.

The racetrack logic technology can have a strong impact on all portable electronic devices like IoT nodes, tablets, PC or smartphones. Indeed, the aim of device manufacturers is not only to achieve higher performance, but also to increase the battery life of their products.