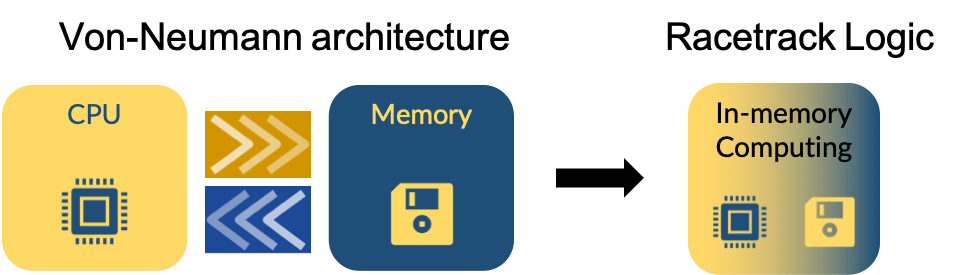

L’attuale paradigma impiegato nelle architetture classiche degli attuali PC e Smartphone è ad oggi vincolata allo schema Von-Neumann in cui sono presenti due componenti principali: la CPU e la memoria. Questa organizzazione implica un continuo scambio di dati tra questi due elementi comportando una limitazione delle prestazioni e elevati consumi di potenza.

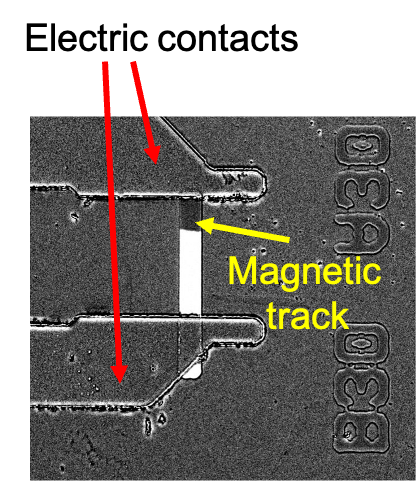

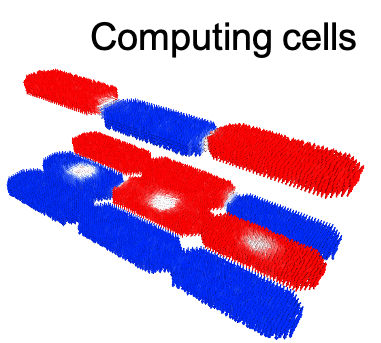

Si propone una nuova memoria magnetica, denominata racetrack logic, di tipo non volatile, capace di realizzare funzioni logiche direttamente sui dati memorizzati. Il dispositivo implementa quindi funzioni che una normale memoria non è in grado di eseguire. Le operazioni logiche possono essere eseguite in parallelo su tutti i dati memorizzati, senza la necessità di usare circuiti addizionali. I dati possono essere movimentati in una direzione e possono essere letti e scritti mediante l’utilizzo di elementi esterni. Questo permette alla memoria di essere utilizzata sia come elemento di memoria che come elemento di calcolo.

La possibilità di poter elaborare in dati in loco permette di ridurre drasticamente il trasferimento di dati tra CPU e memoria, specialmente per applicazioni «data intensive». Il continuo trasferimento di dati tra memoria e CPU ha un costo energetico molto elevato.

L’impatto della tecnologia è molto vasto, include tutti i dispositivi IoT, PC, tablet e smartphone. Infatti, i produttori di questi dispositivi hanno come obiettivo quello di massimizzare la durata della batteria, oltre che mantenere un elevato livello di prestazioni.